## **FEATURES**

- 1 to 1.6 Gigabits Per Second (Gbps) Serializer/Deserializer (TLK2201)

- 1.2 to 1.6 Gigabits Per Second (Gbps) Serializer/Deserializer (TLK2201I)

- Low Power Consumption <200 mW at 1.25 Gbps

- LVPECL Compatible Differential I/O on High Speed Interface

- Single Monolithic PLL Design

- Support For 10 Bit Interface or Reduced Interface 5 Bit DDR (Double Data Rate) Clocking

- Receiver Differential Input Thresholds 200 mV Minimum

- Industrial Temperature Range From -40°C to 85°C (TLK2201I)

- IEEE 802.3 Gigabit Ethernet Compliant

- Advanced 0.25 µm CMOS Technology

- No External Filter Capacitors Required

- Comprehensive Suite of Built-In Testability

- IEEE 1149.1 JTAG Support

- 2.5-V Supply Voltage for Lowest Power Operation

- 3.3-V Tolerant on LVTTL Inputs

- Hot Plug Protection

- 64-Pin VQFP With Thermally Enhanced Package (PowerPAD™)

## **DESCRIPTION**

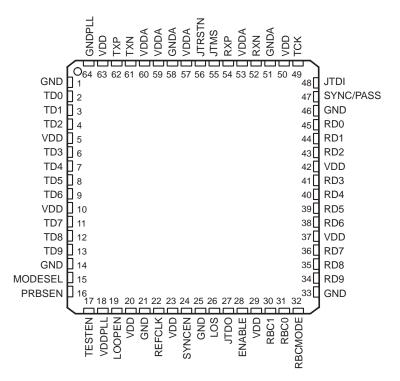

The TLK2201 and TLK2201I gigabit ethernet transceivers provide for ultrahigh-speed full-duplex point-to-point data transmissions. These devices are based on the timing requirements of the 10-bit interface specification by the IEEE 802.3 Gigabit Ethernet specification. The TLK2201 supports data rates from 1.0 Gbps through 1.6 Gbps and the TLK2201I supports data rates from 1.2 Gbps through 1.6 Gbps.

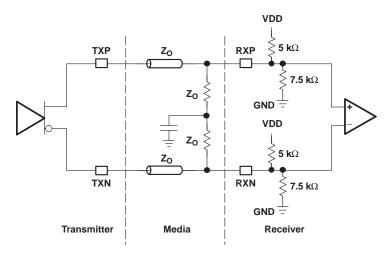

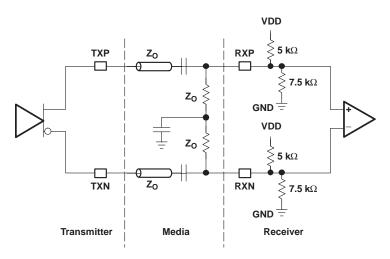

The primary application of these devices is to provide building blocks for point-to-point baseband data transmission over controlled impedance media of 50  $\Omega$  or 75  $\Omega$ . The transmission media can be printed-circuit board traces, copper cables or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

SLLS420F-JUNE 2000-REVISED SEPTEMBER 2007

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **DESCRIPTION CONTINUED**

The TLK2201 and TLK2201I perform the data serialization, deserialization, and clock extraction functions for a physical layer interface device. The transceiver operates at 1.25 Gbps (typical), providing up to 1 Gbps of data bandwidth over a copper or optical media interface.

The TLK2201 and TLK2201I support both the defined 10-bit interface (TBI) and a reduced 5-bit interface utilizing double data rate (DDR) clocking. In the TBI mode the serializer/deserializer (SERDES) accepts 10-bit wide 8b/10b parallel encoded data bytes. The parallel data bytes are serialized and transmitted differentially at PECL compatible voltage levels. The SERDES extracts clock information from the input serial stream and deserializes the data, outputting a parallel 10-bit data byte.

In the DDR mode the parallel interface accepts 5-bit wide 8b/10b encoded data aligned to both the rising and falling edge of the reference clock. The data is clocked most significant bit first, (bits 0 - 4 of the 8b/10b encoded data) on the rising edge of the clock and the least significant bits (bits 5 - 9 of the 8b/10b encoded data) are clocked on the falling edge of the clock.

The TLK2201 and TLK2201I provide a comprehensive series of built-in tests for self-test purposes including loopback and pseudorandom binary sequence (PRBS) generation and verification. An IEEE 1149.1 JTAG port is also supported.

The TLK2201 and TLK2201I are housed in a high performance, thermally enhanced, 64-pin VQFP PowerPAD package. Use of the PowerPAD package does not require any special considerations except to note that the PowerPAD, which is an exposed die pad on the bottom of the device, is a metallic thermal and electrical conductor. It is recommended that the TLK2201 and TLK2201I PowerPADsbe soldered to the thermal land on the board.

The TLK2201 is characterized for operation from 0°C to 70°C. The TLK2201I is characterized for operation from -40°C to 85°C.

The TLK2201 and TLK2201I use a 2.5-V supply. The I/O section is 3.3-V compatible. With the 2.5-V supply the chipset is very power-efficient, dissipating less than 200 mW typical power when operating at 1.25 Gbps.

The TLK2201 and TLK2201I are designed to be hot plug capable. A power-on reset causes RBC0, RBC1, the parallel output signal terminals, TXP, and TXN to be held in high-impedance state.

## Differences Between TLK2201, TLK2201I, and TNETE2201

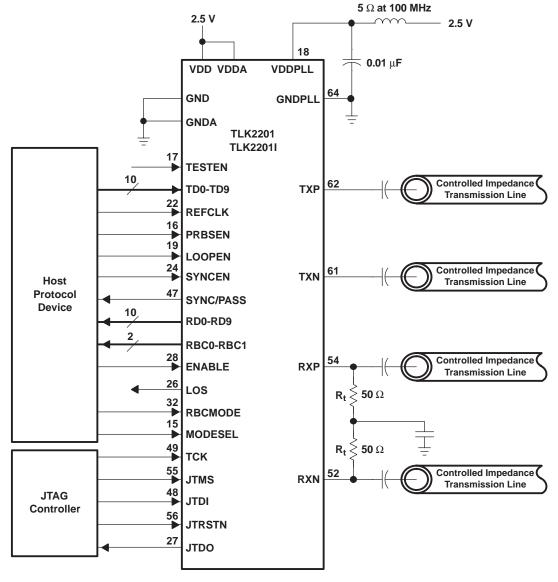

The TLK2201 and TLK2201I are the functional equivalent of the TNETE2201. There are several differences between the devices as noted below. See Figure 12 in the application information section for an example of a typical application circuit.

- The V<sub>CC</sub> is 2.5 V for the TLK2201 and TLK2201I vs 3.3 V for TNETE2201.

- The PLL filter capacitors on pins 16, 17, 48, and 49 of the TNETE2201 are no longer required. The TLK2201 and TLK2201I uses these pins to provide added test capabilities. The capacitors, if present, do not affect the operation of the device.

- No pulldown resistors are required on the TXP/TXN outputs.

#### **AVAILABLE OPTIONS**

| T <sub>A</sub> | PACKAGE <sup>(1)</sup>       |

|----------------|------------------------------|

|                | PLASTIC QUAD FLAT PACK (RCP) |

| 0°C to 70°C    | TLK2201RCP                   |

| 40°C to 85°C   | TLK2201IRCP                  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

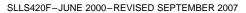

#### **Terminal Functions**

| TERMINAL |                                                 | I/O       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.                                             | 1/0       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Signal   |                                                 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TXP TXN  | 62 61                                           | PECL<br>O | Differential output transmit. TXP and TXN are differential serial outputs that interface to a copper or an optical I/F module. TXP and TXN are put in a high-impedance state when LOOPEN is high and are active when LOOPEN is low.                                                                                                                                                                                                                                                                                                                                          |

| RXP RXN  | 54 52                                           | PECL I    | Differential input receive. RXP and RXN together are the differential serial input interface from a copper or an optical I/F module.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| REFCLK   | 22                                              | I         | Reference clock. REFCLK is an external input clock that synchronizes the receiver and transmitter interface (100 MHz to 160 MHz). The transmitter uses this clock to register the input data (TD0-TD9) for serialization. In the TBI mode that data is registered on the rising edge of REFCLK. In the DDR mode, the data is registered on both the rising and falling edges of REFCLK with the most significant bits aligned to the rising edge of REFCLK.                                                                                                                  |

| TD0-TD9  | 2-4, 6-9,<br>11-13                              | I         | Transmit data. When in the TBI mode (MODESEL = low) these inputs carry 10-bit parallel data output from a protocol device to the transceiver for serialization and transmission. This 10-bit parallel data is clocked into the transceiver on the rising edge of REFCLK and transmitted as a serial stream with TD0 sent as the first bit. When in the DDR mode (MODESEL = high) only TD0-TD4 are valid. The 5-bit parallel data is clocked into the transceiver on the rising and falling edge of REFCLK and transmitted as a serial stream with TD0 sent as the first bit. |

| RD0-RD9  | 45, 44, 43,<br>41, 40, 39,<br>38, 36, 35,<br>34 | 0         | Receive data. When in TBI mode (MODESEL = low) these outputs carry 10-bit parallel data output from the transceiver to the protocol layer. The data is referenced to terminals RBC0 and RBC1, depending on the receive clock mode selected. RD0 is the first bit received. When in the DDR mode (MODESEL = high) only RD0-RD4 are valid. RD5-RD9 are held low. The 5-bit parallel data is clocked out of the transceiver on the rising edge of RBC0.                                                                                                                         |

# **Terminal Functions (continued)**

| TERMINAL  |                                         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.                                     | 1/0                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RBC0 RBC1 | 31 30                                   | 0                       | Receive byte clock. RBC0 and RBC1 are recovered clocks used for synchronizing the 10-bit output data on RD0-RD9. The operation of these clocks is dependent upon the receive clock mode selected. In the half-rate mode, the 10-bit output data words are valid on the rising edges of RBC0 and RBC1. These clocks are adjusted to half-word boundaries in conjunction with synchronous detect. The clocks are always expanded during data realignment and never slivered or truncated. RBC0 registers bytes 1 and 3 of received data. RBC1 registers bytes 0 and 2 of received data. In the normal rate mode, only RBC0 is valid and operates at 1/10 the serial data rate. Data is aligned to the rising edge. In the DDR mode, only RBC0 is valid and operates at 1/10 the serial data rate. Data is aligned to both the rising and falling edges. |

| RBCMODE   | 32                                      | I<br>P/D <sup>(1)</sup> | Receive clock mode select. When RBCMODE and MODESEL are low, half-rate clocks are output on RBC0 and RBC1. When MODESEL is low and RBCMODE is high, a full baud-rate clock is output on RBC0 and RBC1 is held low. When MODESEL is high, RBCMODE is ignored and a full baud-rate clock is output on RBC0 and RBC1 is held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SYNCEN    | 24                                      | I<br>P/U <sup>(2)</sup> | Synchronous function enable. When SYNCEN is high, the internal synchronization function is activated. When this function is activated, the transceiver detects the K28.5 comma character (0011111 negative beginning disparity) in the serial data stream and realigns data on byte boundaries if required. When SYNCEN is low, serial input data is unframed in RD0 - RD9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SYNC/PASS | 47                                      | 0                       | Synchronous detect. The SYNC output is asserted high upon detection of the comma pattern in the serial data path. SYNC pulses are output only when SYNCEN is activated (asserted high). In PRBS test mode (PRBSEN=high), SYNC/PASS outputs the status of the PRBS test results (high=pass).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LOS       | 26                                      | 0                       | Loss of signal. Indicates a loss of signal on the high-speed differential inputs RXP and RXN. If magnitude of RXP-RXN > 150 mV, LOS = 1, valid input signallf magnitude of RXP-RXN < 150 mV and > 50 mV, LOS is undefined ff magnitude of RXP-RXN < 50 mV, LOS = 0, loss of signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MODESEL   | 15                                      | I<br>P/D <sup>(3)</sup> | Mode select. This terminal selects between the 10-bit interface and a reduced 5-bit DDR interface. When low the 10-bit interface (TBI) is selected. When pulled high, the 5-bit DDR mode is selected. The default mode is the TBI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TEST      |                                         | 1                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LOOPEN    | 19                                      | I<br>P/D <sup>(3)</sup> | Loop enable. When LOOPEN is high (active), the internal loop-back path is activated. The transmitted serial data is directly routed to the inputs of the receiver. This provides a self-test capability in conjunction with the protocol device. The TXP and TXN outputs are held in a high-impedance state during the loop-back test. LOOPEN is held low during standard operational state with external serial outputs and inputs active.                                                                                                                                                                                                                                                                                                                                                                                                           |

| TCK       | 49                                      | I                       | Test clock. IEEE1149.1 (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| JTDI      | 48                                      | I<br>P/U <sup>(4)</sup> | Test data input. IEEE1149.1 (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| JTDO      | 27                                      | 0                       | Test data output. IEEE1149.1 (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| JTRSTN    | 56                                      | I<br>P/U <sup>(4)</sup> | Reset signal. IEEE1149.1 (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| JTMS      | 55                                      | I<br>P/U <sup>(4)</sup> | Test mode select. IEEE1149.1 (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ENABLE    | 28                                      | I<br>P/U <sup>(4)</sup> | When this terminal is low, the device is disabled for Iddq testing. RD0 - RD9, RBCn, TXP, and TXN are high impedance. The pullup and pulldown resistors on any input are disabled. When ENABLE is high, the device operates normally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PRBSEN    | 16                                      | I<br>P/D <sup>(3)</sup> | PRBS enable. When PRBSEN is high, the PRBS generation circuitry is enabled. The PRBS verification circuit in the receive side is also enabled. A PRBS signal can be fed to the receive inputs and checked for errors, that are reported by the SYNC/PASS terminal indicating low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TESTEN    | 17                                      | I<br>P/D <sup>(3)</sup> | Manufacturing test terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| POWER     |                                         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDD       | 5, 10, 20,<br>23, 29, 37,<br>42, 50, 63 | Supply                  | Digital logic power. Provides power for all digital circuitry and digital I/O buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDDA      | 53, 57, 59,<br>60                       | Supply                  | Analog power. VDDA provides power for the high-speed analog circuits, receiver, and transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

- (1) P/D = Internal pulldown

(2) P/U = Internal pullup

(3) P/D = Internal pulldown

- (4) P/U = Internal pullup

## **Terminal Functions (continued)**

| TERMINAL |                            | 1/0    | DESCRIPTION                                                                                   |

|----------|----------------------------|--------|-----------------------------------------------------------------------------------------------|

| NAME     | NO.                        | I/O    | DESCRIPTION                                                                                   |

| VDDPLL   | 18                         | Supply | PLL power. Provides power for the PLL circuitry. This terminal requires additional filtering. |

| GROUND   |                            |        |                                                                                               |

| GNDA     | 51,58                      | Ground | Analog ground. GNDA provides a ground for the high-speed analog circuits, RX and TX.          |

| GND      | 1, 14,<br>21,25, 33,<br>46 | Ground | Digital logic ground. Provides a ground for the logic circuits and digital I/O buffers.       |

| GNDPLL   | 64                         | Ground | PLL ground. Provides a ground for the PLL circuitry.                                          |

#### **DETAILED DESCRIPTION**

#### **Data Transmission**

These devices support both the defined 10-bit interface (TBI) and a reduced 5-bit interface utilizing DDR clocking. When MODESEL is low, the TBI mode is selected. When MODESEL is high, the DDR mode is selected.

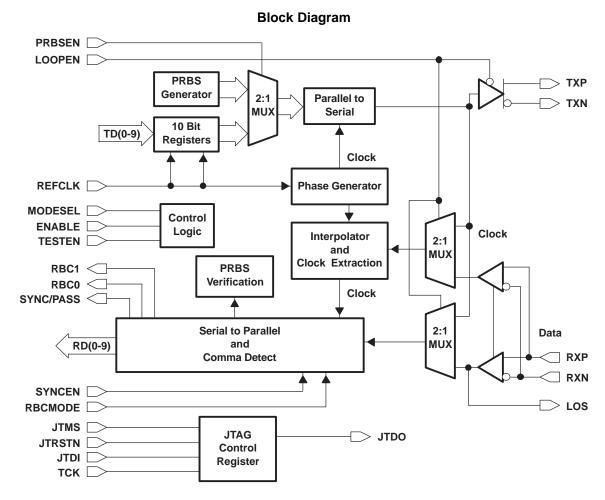

In the TBI mode, the transmitter portion registers incoming 10-bit wide data words (8b/10b encoded data, TD0-TD9) on the rising edge of REFCLK. The REFCLK is also used by the serializer, which multiplies the clock by a factor of 10, providing a signal that is fed to the shift register. The 8b/10b encoded data is transmitted sequentially bit 0 through 9 over the differential high-speed I/O channel.

In the DDR mode, the transmitter accepts 5-bit wide 8b/10b encoded data on pins TD0-TD4. In this mode data is aligned to both the rising and falling edges of REFCLK. The data is then formed into a 10-bit wide word and sent to the serializer. The rising edge REFCLK clocks in bit 0-4, and the falling edge of REFCLK clocks in bits 5-9. (Bit 0 is the first bit transmitted).

#### **Transmission Latency**

Data transmission latency is defined as the delay from the initial 10-bit word load to the serial transmission of bit 9. The minimum latency in TBI mode is 19 bit times. The maximum latency in TBI mode is 20 bit times. The minimum latency in DDR mode is 29 bit times, and maximum latency in DDR mode is 30 bit times.

Figure 1. Transmitter Latency Full Rate Mode

## **Data Reception**

The receiver portion deserializes the differential serial data. The serial data is retimed based on an interpolated clock generated from the reference clock. The serial data is then aligned to the 10-bit word boundaries and presented to the protocol controller along with receive byte clocks (RBC0, RBC1).

## **Receiver Clock Select Mode**

There are two modes of operation for the parallel busses. 1)The 10-bit (TBI) mode and 2) 5-bit (DDR) mode. When in TBI mode, there are two user-selectable clock modes that are controlled by the RBCMODE terminal. 1) Full-rate clock on RBC0 and 2) Half-rate clocks on RBC0 and RBC1. When in the DDR mode, only a full-rate clock is available on RBC0; refer to Table 1.

#### **Mode Selection**

| MODESEL | RBCMODE | MODE          | FREQUENCY (TLK2201) | FREQUENCY (TLK2201I) |

|---------|---------|---------------|---------------------|----------------------|

| 0       | 0       | TBI half-rate | 100-125 MHz         | 120-125 MHz          |

| 0       | 1       | TBI full-rate | 100-160 MHz         | 120-160 MHz          |

| 1       | 0       | DDR           | 100-125 MHz         | 120-125 MHz          |

| 1       | 1       | DDR           | 100-125 MHz         | 120-125 MHz          |

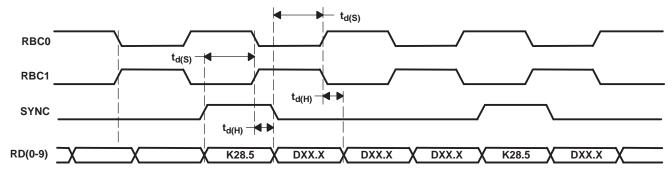

In the half-rate mode, two receive byte clocks (RBC0 and RBC1) are 180 degrees out of phase and operate at one-half the data rate. The clocks are generated by dividing down the recovered clock. The received data is output with respect to the two receive byte clocks (RBC0, RBC1) allowing a protocol device to clock the parallel bytes using the RBC0 and RBC1 rising edges. The outputs to the protocol device, byte 0 of the received data valid on the rising edge of RBC1. See the timing diagram shown in Figure 2.

Figure 2. Synchronous Timing Characteristics Waveforms (TBI half-rate mode)

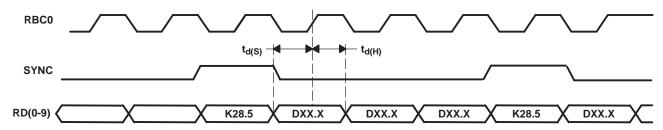

In the normal-rate mode, only RBC0 is used and operates at full data rate (i.e., 1.25 Gbps data rate produces a 125 MHz clock). The received data is output with respect to the rising edge of RBC0. RBC1 is low in this mode. See the timing diagram shown in Figure 3.

Figure 3. Synchronous Timing Characteristics Waveforms (TBI full-rate mode)

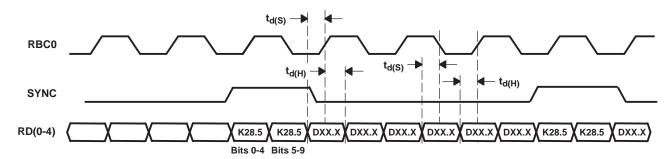

In the double data rate mode, the receiver presents the data on both the rising and falling edges of RBC0. RBC1 is low impedance. The data is clocked bit-0 first, and aligned to the rising edge of RBC0. See the timing diagram shown in Figure 4.

Figure 4. Synchronous Timing Characteristics Waveforms (DDR mode)

The receiver clock interpolator can lock to the incoming data without the need for a lock-to-reference preset. The received serial data rate (RXP and RXN) is at the same baud rate as the transmitted data stream, ±0.02% (200 PPM) for proper operation.

## **Receiver Word Alignment**

These devices use the IEEE 802.3 Gigabit Ethernet defined 10-bit K28.5 character (comma character) word alignment scheme. The following sections explain how this scheme works and how it realigns itself.

## **Comma Character on Expected Boundary**

These devices provide 10-bit K28.5 character recognition and word alignment. The 10-bit word alignment is enabled by forcing the SYNCEN terminal high. This enables the function that examines and compares serial input data to the seven bit synchronization pattern. The K28.5 character is defined by the 8-bit/10-bit coding scheme as a pattern consisting of 0011111010 (a negative number beginning with disparity) with the 7 MSBs (0011111), referred to as the comma character. The K28.5 character was implemented specifically for aligning data words. As long as the K28.5 character falls within the expected 10-bit boundary, the received 10-bit data is properly aligned and data realignment is not required. Figure 2 shows the timing characteristics of RBC0, RBC1, SYNC and RD0-RD9 while synchronized. (Note: the K28.5 character is valid on the rising edge of RBC1).

## **Comma Character Not on Expected Boundary**

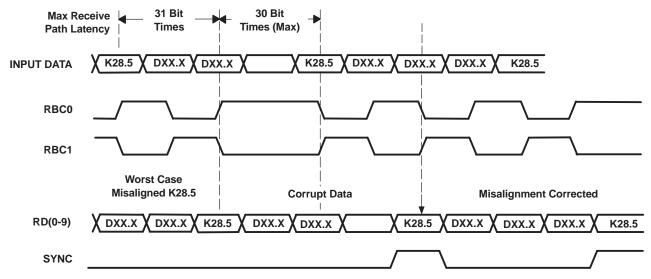

If synchronization is enabled and a K28.5 character straddles the expected 10-bit word boundary, then word realignment is necessary. Realignment or shifting the 10-bit word boundary truncates the character following the misaligned K28.5, but the following K28.5 and all subsequent data is aligned properly as shown in Figure 5. The RBC0 and RBC1 pulse widths are stretched or stalled in their current state during realignment. With this design the maximum stretch that occurs is 20 bit times. This occurs during a worst case scenario when the K28.5 is aligned to the falling edge of RBC1 instead of the rising edge. Figure 5 shows the timing characteristics of the data realignment.

Figure 5. Word Realignment Timing Characteristics Waveforms

Systems that do not require framed data may disable byte alignment by tying SYNCEN low.

When a SYNC character is detected, the SYNC signal is brought high and is aligned with the K28.5 character. The duration of the SYNC pulse is equal to the duration of the data when in TBI mode. When in DDR mode the SYNC pulse is present for the entire RBC0 period.

## **Data Reception Latency**

The serial to parallel data latency is the time from when the first bit arrives at the receiver until it is output in the aligned parallel word with RD0 received as first bit. The minimum latency in TBI mode is 21 bit times and the maximum latency is 31 bit times. The minimum latency in DDR mode is 27 bit times and maximum latency is 34 bit times.

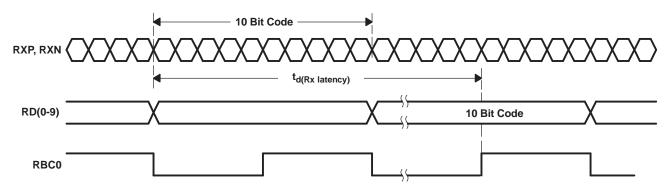

Figure 6. Receiver Latency - TBI Normal Mode Shown

## **Loss of Signal Detection**

These devices have a loss of signal (LOS) detection circuit for conditions where the incoming signal no longer has sufficient voltage level to keep the clock recovery circuit in lock. The LOS is intended to be an indication of gross signal error conditions, such as a detached cable or no signal being transmitted, and not an indication of signal coding health. Under a PRBS serial input pattern, LOS is high for signal amplitudes greater than 150 mV. The LOS is low for all amplitudes below 50 mV. Between 50 mV and 150 mV, LOS is undetermined.

## **Testability**

The loopback function provides for at-speed testing of the transmit/receive portions of the circuitry. The enable function allows for all circuitry to be disabled so that an Iddq test can be performed. The PRBS function also allows for a BIST( built-in self test). The terminal setting, TESTEN high, enables the test mode. The terminal TESTEN has an internal pulldown resistor, so it defaults to normal operation. The TESTEN is only used for factory testing, and is not intended for the end-user.

## **Loopback Testing**

The transceiver can provide a self-test function by enabling (LOOPEN to high level) the internal loopback path. Enabling this function causes serial transmitted data to be routed internally to the receiver. The parallel data output can be compared to the parallel input data for functional verification. (The external differential output is held in a high-impedance state during the loopback testing.)

#### **Enable Function**

When held low, ENABLE disables all quiescent power in both the analog and digital circuitry. This allows an ultralow-power idle state when the link is not active.

#### **PRBS Function**

These devices have a built-in 2<sup>7</sup>-1 PRBS function. When the PRBSEN control bit is set high, the PRBS test is enabled. A PRBS is generated and fed into the 10-bit parallel transmitter input bus. Data from the normal parallel input source is ignored during PRBS test mode. The PRBS pattern is then fed through the transmit circuitry as if it were normal data and sent out to the transmitter. The output can be sent to a (BERT) bit error rate tester or to the receiver of another TLK2201 or TLK2201I. Since the PRBS is not really random and is really a predetermined sequence of ones and zeros, the data can be captured and checked for errors by a BERT. These devices also have a built-in BERT function on the receiver side that is enabled by PRBSEN. It can receive a PRBS pattern and check for errors, and then reports the errors by forcing the SYNC/PASS terminal low. When PRBS is enabled, RBCMODE is ignored. MODESEL must be low for the PRBS verifier to function correctly. The device operates in TBI mode with a full-rate clock on RBC0. The PRBS testing supports two modes (normal and latched), which are controlled by the SYNCEN input. When SYNCEN is low, the result of the PRBS bit error rate test is passed to the SYNC/PASS terminal. When SYNCEN is high the result of the PRBS verification is latched on the SYNC/PASS output (i.e., a single failure forces SYNC/PASS to remain low).

## **JTAG**

The TLK2201 supports an IEEE1149.1 JTAG function while maintaining compatibility with the industry standard 64 pin QFP package footprint. In this way, the TLK2201 installed on a board layout that was designed for the industry standard footprint such as for the TNETE2201B. (Provided the supply voltage can be programmed from the older 3.3 V to 2.5 V.) The JTAG pins on the TLK2201 are chosen to either be on the 'vender-unique' pins of the industry standard footprint, or are on pins that were previously power or ground. The TRSTN pin has been placed on pin 56, which is a ground on the industry standard footprint. In this way, a TLK2201 installed onto the older footprint has the JTAG tap controller held in reset, and thus disabled. If the JTAG function is desired, then the 5 JTAG pins TRSTN, TMS, TCK, TDI, and TDO can be used in the usual manner for a JTAG function. If the JTAG function is not desired, then connecting TRSTN to ground is recommended. TMS and TDI have internal pullup resistors, and can thus be left unconnected if not used. TDO is an output and should be left unconnected if JTAG is not used. TCK does not have an internal pullup, and can be tied to GND or PWR if not used, but with TRSTN low, this input is not used, and thus can be left unconnected.

SLLS420F-JUNE 2000-REVISED SEPTEMBER 2007

## ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature (unless otherwise noted)

|                                                      |          | UNIT                             |

|------------------------------------------------------|----------|----------------------------------|

| Supply voltage, V <sub>DD</sub> <sup>(2)</sup>       |          | -0.3 V to 3 V                    |

| Input voltage range at TTL terminals, V <sub>I</sub> |          | -0.5 V to 4 V                    |

| Input voltage range at any other terminal            |          | -0.3 V to V <sub>DD</sub> +0.3 V |

| Storage temperature, T <sub>stg</sub>                |          | -65°C to 150°C                   |

| Electrostatic discharge                              |          | CDM: 1 kV, HBM:2 kV              |

| Characterized free air enerating temperature range:  | TLK2201  | 0°C to 70°C                      |

| Characterized free-air operating temperature range:  | TLK2201I | -40°C to 85°C                    |

<sup>(1)</sup> Stresses beyond those listed under, absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under, recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

## **DISSIPATION RATING TABLE**(1)

| PACKAGE              | T <sub>A</sub> ≤ 25°C<br>POWER RATING | OPERATING FACTOR <sup>(2)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|----------------------|---------------------------------------|----------------------------------------------------------------|---------------------------------------|

| RCP64 <sup>(3)</sup> | 5.25 W                                | 46.58 mW/°C                                                    | 2.89 W                                |

| RCP64 <sup>(4)</sup> | 3.17 W                                | 23.70 mW/°C                                                    | 1.74 W                                |

| RCP64 <sup>(5)</sup> | 2.01 W                                | 13.19 mW/°C                                                    | 1.11 W                                |

- (1) For more information, refer to TI application note PowerPAD Thermally Enhanced Package, TI literature number SLMA002.

- (2) This is the inverse of the traditional junction-to-ambient thermal resistance (R<sub>O,IA</sub>).

- 3) 2 oz. Trace and copper pad with solder.

- (4) 2 oz. Trace and copper pad without solder.

- (5) Standard JEDEC high-K board

## THERMAL CHARACTERISTICS

| PARAM            | METER                                   | TEST CONDITION                                                                                                                                       | MIN TYP | MAX | UNIT |  |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|--|

| R <sub>⊝JA</sub> |                                         | Board-mounted, no air flow, high conductivity TI recommended test board, chip soldered or greased to thermal land                                    | 21.47   |     |      |  |

|                  | Junction-to-free-air thermal resistance | Board-mounted, no air flow, high conductivity TI recommended test board with thermal land but no solder or grease thermal connection to thermal land | 42.20   |     | °C/W |  |

|                  |                                         | Board-mounted, no air flow, JEDEC test board                                                                                                         | 75.83   |     |      |  |

|                  | Junction-to-case-thermal resistance     | Board-mounted, no air flow, high conductivity TI recommended test board, chip soldered or greased to thermal land                                    | 0.38    |     | °C/W |  |

| $R_{\Theta JC}$  |                                         | Board-mounted, no air flow, high conductivity TI recommended test board with thermal land but no solder or grease thermal connection to thermal land | 0.38    |     |      |  |

|                  |                                         | Board-mounted, no air flow, JEDEC test board                                                                                                         | 7.8     |     |      |  |

## RECOMMENDED OPERATING CONDITIONS

|                                                            |                                                                 | MIN | NOM | MAX | UNIT |  |

|------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|------|--|

| Supply voltage, V <sub>DD,</sub> V <sub>DD(A)</sub>        |                                                                 | 2.3 | 2.5 | 2.7 | V    |  |

| Total augusts augusts I                                    | Frequency = 1.25 Gbps, PRBS pattern                             |     | 80  |     | A    |  |

| Total supply current I <sub>DD</sub> ,I <sub>DD</sub> (A)  | Frequency = 1.6 Gbps, Worst case pattern <sup>(1)</sup>         |     |     | 111 | mA   |  |

| T                                                          | Frequency = 1.25 Gbps PRBS pattern                              |     | 200 |     | \^/  |  |

| Total power dissipation P <sub>D</sub>                     | Frequency = 1.6 Gbps Worst case pattern <sup>(1)</sup>          |     |     | 310 | mW   |  |

| Total shutdown current I <sub>DD</sub> ,I <sub>DD(A)</sub> | Enable = 0, Vdda , Vdd = 2.7 V                                  |     |     | 50  | μΑ   |  |

| Startup lock time, PLL                                     | V <sub>DD,</sub> V <sub>DD(A)</sub> = 2.5 V, EN↑ to PLL acquire |     |     | 500 | μs   |  |

| Operating free air temperature T                           | TLK2201                                                         | 0   |     | 70  | °C   |  |

| Operating free-air temperature, T <sub>A</sub>             | TLK2201I                                                        | 40  |     | 85  | ٠.   |  |

<sup>(1)</sup> Worst case pattern is a pattern that creates a maximum transition density on the serial transceiver.

## TLK2201 REFERENCE CLOCK (REFCLK) TIMING REQUIREMENTS

over recommended operating conditions (unless otherwise noted)

| PARAMETER  | TEST CONDITIONS           | MIN       | TYP | MAX       | UNIT |

|------------|---------------------------|-----------|-----|-----------|------|

| Frequency  | Minimum data rate         | TYP-0.01% | 100 | TYP-0.01% | MHz  |

| Frequency  | Maximum data rate         | TYP-0.01% | 160 | TYP-0.01% | MHz  |

| Accuracy   |                           | 100       |     | 100       | ppm  |

| Duty cycle |                           | 40%       | 50% | 60%       |      |

| Jitter     | Random plus deterministic |           |     | 40        | ps   |

## TLK2201I REFERENCE CLOCK (REFCLK) TIMING REQUIREMENTS

over recommended operating conditions (unless otherwise noted)

| PARAMETER  | TEST CONDITIONS           | MIN       | TYP | MAX       | UNIT |

|------------|---------------------------|-----------|-----|-----------|------|

| Frequency  | Minimum data rate         | TYP-0.01% | 120 | TYP-0.01% | MHz  |

| Frequency  | Maximum data rate         | TYP-0.01% | 160 | TYP-0.01% | MHz  |

| Accuracy   |                           | 100       |     | 100       | ppm  |

| Duty cycle |                           | 40%       | 50% | 60%       |      |

| Jitter     | Random plus deterministic |           |     | 40        | ps   |

## TTL ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

| PARA            | METER                     | TEST CONDITIONS                                  | MIN                  | TYP  | MAX | UNIT |

|-----------------|---------------------------|--------------------------------------------------|----------------------|------|-----|------|

| $V_{OH}$        | High-level output voltage | I <sub>OH</sub> = -400 μA                        | V <sub>DD</sub> -0.2 | 2.3  |     | V    |

| V <sub>OL</sub> | Low-level output voltage  | I <sub>OL</sub> = 1 mA                           | GND                  | 0.25 | 0.5 | V    |

| $V_{IH}$        | High-level input voltage  |                                                  | 1.7                  |      | 3.6 | V    |

| $V_{IL}$        | Low-level input voltage   |                                                  |                      |      | 8.0 | V    |

| I <sub>IH</sub> | Input high current        | $V_{DD} = 2.3 \text{ V}, V_{IN} = 2.0 \text{ V}$ |                      |      | 40  | μA   |

| I <sub>IL</sub> | Input low current         | $V_{DD} = 2.3 \text{ V}, V_{IN} = 0.4 \text{ V}$ | -40                  |      |     | μΑ   |

| C <sub>IN</sub> |                           |                                                  |                      |      | 4   | pf   |

## TRANSMITTER/RECEIVER CHARACTERISTICS

| PARAMETER                       |                                                                                |                                                                                          | TEST CONDITIONS                                                           | MIN           | TYP  | MAX  | UNIT      |  |  |

|---------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------|------|------|-----------|--|--|

|                                 | \/  TD. TNII                                                                   |                                                                                          | Rt = 50 Ω                                                                 | 600           | 850  | 1100 | \/        |  |  |

|                                 | Vod =  TxD-TxN                                                                 |                                                                                          | Rt = 75 Ω                                                                 | 800 1050 1200 |      |      | mV        |  |  |

|                                 | Transaction and a college was a                                                | Rt = 50 Ω                                                                                | 1000                                                                      | 1250          | 1400 | mV   |           |  |  |

| $V_{(cm)}$                      | Transmit common mode voltage range                                             | ;                                                                                        | Rt = 75 Ω                                                                 | 1000          | 1250 | 1400 | mv        |  |  |

|                                 | Receiver Input voltage requirement, Vi RxN                                     | id =  RxP -                                                                              |                                                                           | 200           |      | 1600 | mV        |  |  |

|                                 | Receiver common mode voltage range RxN)/2                                      | e, (RxP +                                                                                |                                                                           | 1000          | 1250 | 2250 | mV        |  |  |

| I <sub>lkg(R)</sub>             | Receiver input leakage current                                                 |                                                                                          |                                                                           | 350           |      | 350  | μΑ        |  |  |

| C <sub>I</sub>                  | Receiver input capacitance                                                     |                                                                                          |                                                                           |               | 2    | pF   |           |  |  |

| t <sub>(TJ)</sub>               | Serial data total jitter (peak-to-peak)                                        | Differential output jitter, Random + deterministic, PRBS pattern, $R_{\omega}$ = 125 MHz |                                                                           |               | 0.24 | UI   |           |  |  |

| t <sub>(DJ)</sub>               | Serial data deterministic jitter (peak-to-                                     | -peak)                                                                                   | Differential output jitter, PRBS pattern, $R_{\omega}$ = 125 MHz          |               |      | 0.12 | UI        |  |  |

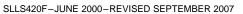

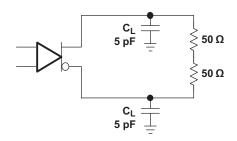

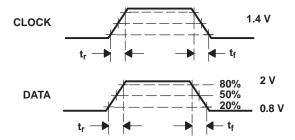

| t <sub>r</sub> , t <sub>f</sub> | Differential signal rise, fall time (20% to                                    | o 80%)                                                                                   | $R_L = 50 \Omega$ , $C_L = 5 pF$ , See Figure 9 and Figure 10             | 100           |      | 250  | ps        |  |  |

|                                 | Serial data jitter tolerance minimum recopening, (per IEEE-802.3 specification |                                                                                          | Differential input jitter, Random + deterministic, $R_{\omega}$ = 125 MHz | 0.25          |      |      | UI        |  |  |

|                                 | Receiver data acquisition lock time from                                       |                                                                                          |                                                                           |               | 500  | μs   |           |  |  |

|                                 | Data relock time from loss of synchron                                         | ata relock time from loss of synchronization                                             |                                                                           |               |      | 1024 | Bit times |  |  |

| +                               | Tx latency                                                                     | See Figure 1                                                                             | 19                                                                        |               | 20   | UI   |           |  |  |

| t <sub>d(Tx latency)</sub>      | DD                                                                             | R mode                                                                                   |                                                                           | 29            |      | 30   | UI UI     |  |  |

|                                 | TB TB                                                                          | See Figure 6                                                                             | 21                                                                        |               | 31   | UI   |           |  |  |

| t <sub>d(Rx latency)</sub>      | Rx latency DD                                                                  | R mode                                                                                   |                                                                           | 27            |      | 34   | UI        |  |  |

Figure 7. Differential and Common-Mode Output Voltage Definitions

**TLK2201**

Figure 8. Transmitter Test Setup

## LVTTL OUTPUT SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

| PARAM               | IETER                                                        | TEST CONDITIONS                                           | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| t <sub>r(RBC)</sub> | Clock rise time                                              |                                                           | 0.3 |     | 1.5 |      |

| t <sub>f(RBC)</sub> | Clock fall time                                              | 80% to 20% output voltage, C = 5 pF (see Figure 9)        |     |     | 1.5 | ns   |

| t <sub>r</sub>      | Data rise time                                               |                                                           |     |     | 1.5 |      |

| t <sub>f</sub>      | Data fall time                                               |                                                           |     |     | 1.5 | ns   |

| t <sub>su(D1)</sub> | Data setup time (RD0RD9),<br>Data valid prior to RBC0 rising | TBI normal mode (see Figure 3)                            | 2.5 |     |     | ns   |

| t <sub>h(D1)</sub>  | Data hold time (RD0RD9),<br>Data valid after RBC0 rising     | TBI normal mode (see Figure 3)                            | 2   |     |     | ns   |

| t <sub>su(D2)</sub> | Data setup time (RD0RD4)                                     | DDR mode, $R_{\omega}$ = 125 MHz (see Figure 4)           | 2   |     |     | ns   |

| t <sub>h(D2)</sub>  | Data hold time (RD0RD4)                                      | DDR mode, $R_{\omega}$ = 125 MHz (see Figure 4)           | 0.8 |     |     | ns   |

| t <sub>su(D3)</sub> | Data setup time (RD0RD9)                                     | TBI half-rate mode, $R_{\omega}$ = 125 MHz (see Figure 2) | 2.5 |     |     | ns   |

| t <sub>h(D3)</sub>  | Data hold time (RD0RD9)                                      | TBI half-rate mode, $R_{\omega} = 125$ MHz (see Figure 2) | 1.5 |     |     | ns   |

Figure 9. TTL Data I/O Valid Levels for AC Measurement

## TRANSMITTER TIMING REQUIREMENTS

over recommended operating conditions (unless otherwise noted)

| PARAMETER           |                                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|---------------------------------|-----------------|-----|-----|-----|------|

| t <sub>su(D4)</sub> | Data setup time (TD0TD9)        | TBI modes       | 1.6 |     |     | no   |

| t <sub>h(D4)</sub>  | Data hold time (TD0TD9)         | 1 bi modes      | 0.8 |     |     | ns   |

| t <sub>su(D5)</sub> | Data setup time (TD0TD9)        | DDR modes       | 0.7 |     |     | no   |

| t <sub>h(D5)</sub>  | Data hold time (TD0TD9)         | DDR Illodes     | 0.5 |     |     | ns   |

| $t_r, t_f$          | TD[0,9] Data rise and fall time | See Figure 11   |     |     | 2   | ns   |

## **APPLICATION INFORMATION**

#### 8B/10B Transmission Code

The PCS maps GMII signals into ten-bit code groups and vice versa, using an 8b/10b block coding scheme. The PCS uses the transmission code to improve the transmission characteristics of information to be transferred across the link. The encoding defined by the transmission code ensures that sufficient transitions are present in the PHY bit stream to make clock recovery possible in the receiver. Such encoding also greatly increases the likelihood of detecting any single or multiple bit errors that may occur during transmission and reception of information. The 8b/10b transmission code specified for use has a high transition density, is run length limited, and is dc-balanced. The transition density of the 8b/10b symbols ranges from 3 to 8 transitions per symbol. The definition of the 8b/10b transmission code is specified in IEEE 802.3 Gigabit Ethernet and ANSI X3.230-1994 (FC-PH), clause 11.

8b/10b transmission code uses letter notation describing the bits of an unencoded information octet. The bit notation of A,B,C,D,E,F,G,H for an unencoded information octet is used in the description of the 8b/10b transmission code-groups, where A is the LSB. Each valid code group has been given a name using the following convention: /Dx.y/ for the 256 valid data code-groups and /Kx.y/ for the special control code-groups, where y is the decimal value of bits EDCBA and x is the decimal value of bits HGF (noted as K<HGF.EDCBA>). Thus, an octet value of FE representing a code-group value of K30.7 would be represented in bit notation as 111 11110.

Figure 10. High-Speed I/O Directly-Coupled Mode

Figure 11. High-Speed I/O AC-Coupled Mode

Figure 12. Typical Application Circuit (AC mode)

## **Designing With PowerPAD™**

The TLK2201 and TLK2201I are housed in a high performance, thermally enhanced, 64-pin VQFP (RCP64) PowerPAD package. Use of the PowerPAD package does not require any special considerations except to note that the PowerPAD, which is an exposed die pad on the bottom of the device, is a metallic thermal and electrical conductor. Therefore, if not implementing PowerPAD PCB features, the use of solder masks (or other assembly techniques) may be required to prevent any inadvertent shorting by the exposed PowerPAD of connection etches or vias under the package. It is strongly recommended that the PowerPAD be soldered to the thermal land. The recommended convention, however, is to not run any etches or signal vias under the device, but to have only a grounded thermal land as explained below. Although the actual size of the exposed die pad may vary, the minimum size required for the keepout area for the 64-pin PFP PowerPAD package is 8 mm 18 mm.

It is recommended that there be a thermal land, which is an area of solder-tinned-copper, underneath the PowerPAD package. The thermal land varies in size depending on the PowerPAD package being used, the PCB construction, and the amount of heat that needs to be removed. In addition, the thermal land may or may not contain numerous thermal vias depending on PCB construction.

SLLS420F-JUNE 2000-REVISED SEPTEMBER 2007

Other requirements for thermal lands and thermal vias are detailed in the TI application note *PowerPAD Thermally Enhanced Package Application Report*, TI literature number SLMA002, available via the TI Web pages beginning at URL: http://www.ti.com.

Figure 13. Example of a Thermal Land

For the TLK2201, this thermal land must be grounded to the low-impedance ground plane of the device. This improves not only thermal performance but also the electrical grounding of the device. It is also recommended that the device ground pin landing pads be connected directly to the grounded thermal land. The land size must be as large as possible without shorting device signal pins. The thermal land may be soldered to the exposed PowerPAD using standard reflow soldering techniques.

While the thermal land may be electrically floated and configured to remove heat to an external heat sink, *it is recommended* that the thermal land be connected to the low-impedance ground plane for the device. More information may be obtained from the TI application note *PHY Layout*, TI literature number SLLA020.

10-Jun-2014

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TLK2201IRCP      | NRND   | HVQFP        | RCP     | 64   | 160     | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | TLK2201I       |         |

| TLK2201RCP       | NRND   | HVQFP        | RCP     | 64   | 160     | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | 0 to 70      | TLK2201        |         |

| TLK2201RCPR      | NRND   | HVQFP        | RCP     | 64   | 1000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | 0 to 70      | TLK2201        |         |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

## PACKAGE OPTION ADDENDUM

10-Jun-2014

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 14-Jul-2012

## TAPE AND REEL INFORMATION

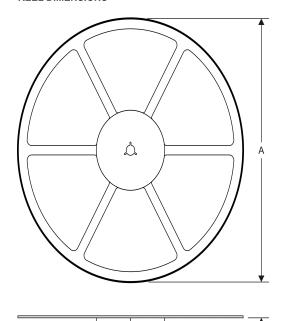

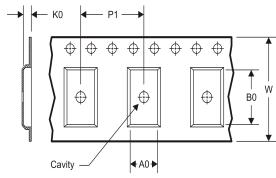

## **REEL DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## TAPE AND REEL INFORMATION

\*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLK2201RCPR | HVQFP           | RCP                | 64 | 1000 | 330.0                    | 24.4                     | 13.0       | 13.0       | 1.5        | 16.0       | 24.0      | Q2               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 14-Jul-2012

#### \*All dimensions are nominal

| I | Device      | Device Package Type |     | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|-------------|---------------------|-----|------|------|-------------|------------|-------------|--|

| I | TLK2201RCPR | HVQFP               | RCP | 64   | 1000 | 367.0       | 367.0      | 45.0        |  |

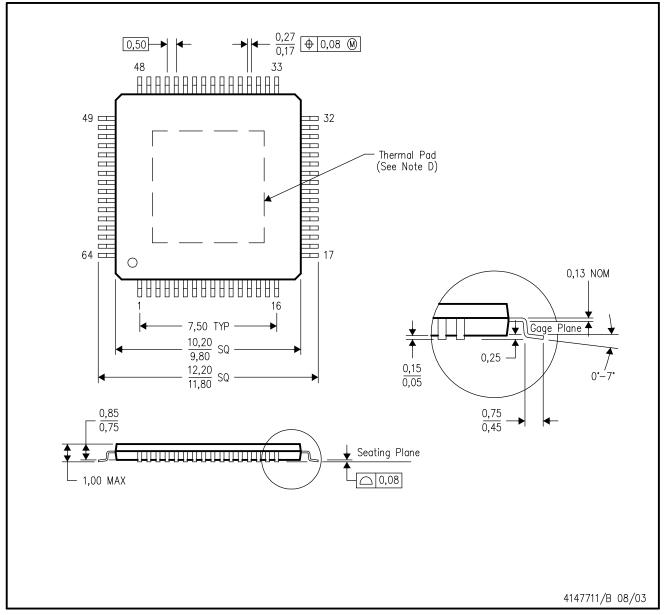

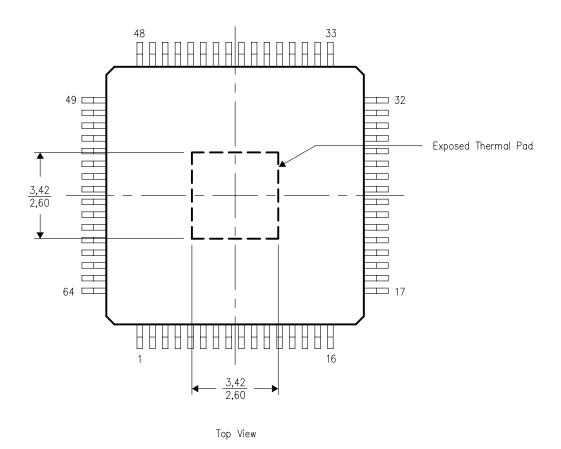

# RCP (S-PQFP-G64)

# PowerPAD™ PLASTIC QUAD FLATPACK

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments.

#### THERMAL INFORMATION

This PowerPAD  $^{\text{TM}}$  package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

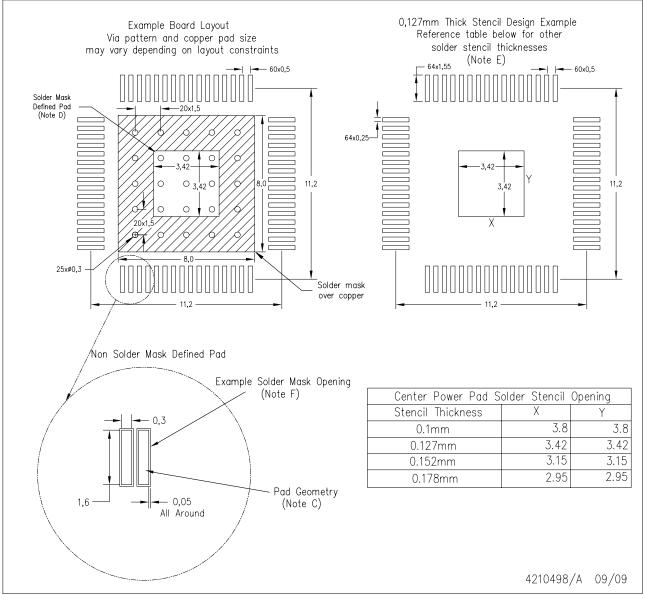

# RCP (R-PVQFN-G64)PowerPAD™

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting options for vias placed in the thermal pad.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.