# Si4825-A10

# BROADCAST MECHANICAL TUNING AM/FM/SW RADIO RECEIVER

#### Features

- Worldwide FM band support (64–109 MHz)

- Worldwide AM band support (504–1750 kHz)

- SW band support (2.3–28.5 MHz)

- No manual alignment necessary

- Mono audio output

- Selectable support AM/FM/SW regional bands

- Enhanced FM/SW band coverage

- Automatic frequency control (AFC)

- Integrated LDO regulator

- 2.0 to 3.6 V supply voltage

- Wide range of ferrite loop sticks and air loop antennas supported

- 16-pin SOIC

Modules

Mini HiFi

Clock radios

- RoHS-compliant

- Direct volume control

- Not EN55020 compliant\*

Entertainment systems

\*Note: For consumer applications that require EN 55020 compliance, use Si483x.

This product, its features, and/or its architecture is covered by one or more of the following patents, as well as other patents, pending and issued, both foreign and domestic: 7,127,217; 7,272,373; 7,272,375; 7,321,324; 7,355,476; 7,426,376; 7,471,940; 7,339,503; 7,339,504.

#### Applications

- Table and portable radios

- Mini/micro systems

- CD/DVD players

- Boom boxes

#### Description

The Si4825 is the entry level mechanical-tuned digital CMOS AM/FM/SW radio receiver IC that integrates the complete receiver function from antenna input to audio output. The Si4825 extends Silicon Laboratories multi-band tuner family, and further increases the ease and attractiveness of design radio reception to audio devices through small size and board area, minimum component count, and superior, proven performance. The Si4825 requires a simple application circuit and removes any requirements for manually tuning components during the manufacturing process. The receiver has very low power consumption, runs off two AAA batteries, and delivers the performance benefits of digital tuning to the analog radio market.

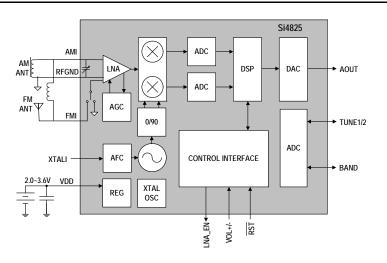

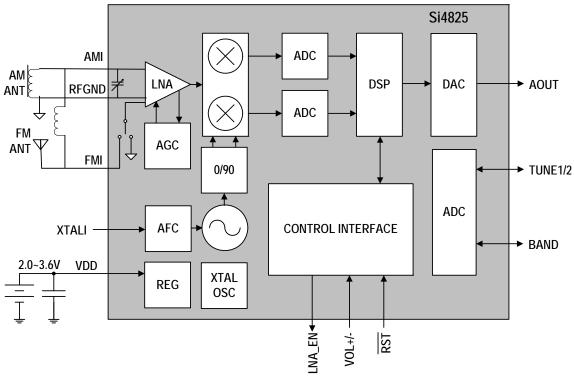

#### **Functional Block Diagram**

Rev. 1.0 5/13

Copyright © 2013 by Silicon Laboratories

Si4825

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Si4825

# TABLE OF CONTENTS

# Section

# <u>Page</u>

| 1. Electrical Specifications       |

|------------------------------------|

| 2. Typical Application Schematic   |

| 3. Bill of Materials               |

| 4. Functional Description          |

| 4.1. Overview                      |

| 4.2. FM Receiver                   |

| 4.3. AM Receiver                   |

| 4.4. SW Receiver                   |

| 4.5. Frequency Tuning              |

| 4.6. Band Select                   |

| 4.7. Volume Control                |

| 4.8. Reset, Powerup, and Powerdown |

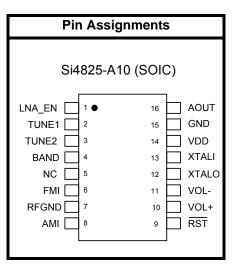

| 5. Pin Descriptions: Si4825-A10    |

| 6. Ordering Guide                  |

| 7. Package Outline: Si4825-A10     |

| 8. PCB Land Pattern: Si4825-A10    |

| 9. Top Marking                     |

| 9.1. Si4825-A10 Top Marking        |

| 9.2. Top Marking Explanation       |

| 10. Additional Reference Resources |

| Document Change List               |

| Contact Information                |

# **1. Electrical Specifications**

### Table 1. Recommended Operating Conditions<sup>1,2</sup>

| Parameter                      | Symbol              | Test Condition | Min | Тур | Max | Unit |

|--------------------------------|---------------------|----------------|-----|-----|-----|------|

| Supply Voltage <sup>3</sup>    | V <sub>DD</sub>     |                | 2   | _   | 3.6 | V    |

| Power Supply Powerup Rise Time | V <sub>DDRISE</sub> |                | 10  | _   | _   | μs   |

| Ambient Temperature Range      | Τ <sub>Α</sub>      |                | 0   | 25  | 70  | °C   |

Note:

1. Typical values in the data sheet apply at V\_DD = 3.3 V and 25  $^\circ\text{C}$  unless otherwise stated.

2. All minimum and maximum specifications in the data sheet apply across the recommended operating conditions for

minimum  $V_{DD}$  = 2.7 V. 3. Operation at minimum  $V_{DD}$  is guaranteed by characterization when  $V_{DD}$  voltage is ramped down to 2.0 V. Part initialization may become unresponsive below 2.3 V.

#### Table 2. DC Characteristics

(V<sub>DD</sub> = 2.7 to 3.6 V, T<sub>A</sub> = 0 to 70 °C)

| Parameter                                                | Symbol            | Test Condition | Min | Тур  | Мах | Unit |

|----------------------------------------------------------|-------------------|----------------|-----|------|-----|------|

| FM Mode                                                  |                   |                |     |      |     |      |

| Supply Current <sup>*</sup>                              | I <sub>FM</sub>   |                | _   | 20.0 | _   | mA   |

| AM/SW Mode                                               |                   |                |     |      |     |      |

| Supply Current*                                          | I <sub>AM</sub>   |                | _   | 19.0 | _   | mA   |

| Supplies and Interface                                   |                   |                |     |      |     |      |

| V <sub>DD</sub> Powerdown Current                        | I <sub>DDPD</sub> |                | _   | 10   | _   | μA   |

| Note: Specifications are guaranteed by characterization. |                   |                |     |      |     |      |

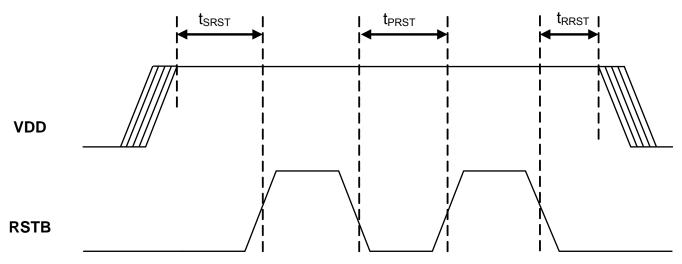

#### Table 3. Reset Timing Characteristics

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ TA} = 0 \text{ to } 70 \text{ °C})$

| Parameter                                | Symbol            | Min | Тур | Max | Unit |

|------------------------------------------|-------------------|-----|-----|-----|------|

| RSTB Pulse Width                         | t <sub>PRST</sub> | 100 | _   | _   | μs   |

| VDD valid time before RSTB rises         | t <sub>SRST</sub> | 100 | —   | —   | μs   |

| RSTB low time before VDD becomes invalid | t <sub>RRST</sub> | 0   | —   | —   | μs   |

| Notes:                                   | ·                 |     |     |     |      |

1. RSTB must be held low for at least 100  $\mu s$  after the voltage supply has been ramped up.

2. RSTB needs to be asserted (pulled low) prior to the supply voltage being ramped down.

Figure 1. Reset Timing

#### Table 4. FM Receiver Characteristics<sup>1,2</sup>

(V<sub>DD</sub> = 2.7 to 3.6 V, TA = 0 to 70 °C)

| Parameter                                          | Symbol          | Test Condition  | Min | Тур | Max | Unit              |

|----------------------------------------------------|-----------------|-----------------|-----|-----|-----|-------------------|

| Input Frequency                                    | f <sub>RF</sub> |                 | 64  | —   | 109 | MHz               |

| Sensitivity with Headphone<br>Network <sup>3</sup> |                 | (S+N)/N = 26 dB |     | 4.0 |     | μV EMF            |

| LNA Input Resistance <sup>4,5</sup>                |                 |                 | _   | 4   | —   | kΩ                |

| LNA Input Capacitance <sup>4,5</sup>               |                 |                 | —   | 5   | —   | pF                |

| AM Suppression <sup>4,5,6,7</sup>                  |                 | m = 0.3         | —   | 50  | —   | dB                |

| Input IP3 <sup>4,8</sup>                           |                 |                 | —   | 105 | _   | dBµV EMF          |

| Adjacent Channel Selectivity <sup>4</sup>          |                 | ±200 kHz        | —   | 45  | _   | dB                |

| Alternate Channel Selectivity <sup>4</sup>         |                 | ±400 kHz        | —   | 60  | _   | dB                |

| Audio Output Voltage <sup>5,6,7</sup>              |                 |                 | _   | 72  | —   | mV <sub>RMS</sub> |

| Audio Mono S/N <sup>5,6,7,9,10</sup>               |                 |                 | —   | 45  | _   | dB                |

| Audio Frequency Response Low <sup>4</sup>          |                 | –3 dB           | —   | —   | 30  | Hz                |

| Audio Frequency Response High <sup>4</sup>         |                 | –3 dB           | 15  | _   | _   | kHz               |

| Audio THD <sup>6,5,11</sup>                        |                 |                 | _   | 0.1 | 0.5 | %                 |

| Audio Output Load Resistance <sup>4,10</sup>       | RL              | Single-ended    | 10  | —   | _   | kΩ                |

| Audio Output Load Capacitance <sup>4,10</sup>      | CL              | Single-ended    | _   |     | 50  | pF                |

Notes:

1. Additional testing information is available in "AN569: Si4831/35/36/20/24/25-DEMO Board Test Procedure." Volume = maximum for all tests. Tested at RF = 98.1 MHz.

2. To ensure proper operation and receiver performance, follow the guidelines in "AN738: Si4825/36-A Antenna, Schematic, Layout, and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 3. Frequency is 64~109 MHz.

- 4. Guaranteed by characterization.

- 5. V<sub>EMF</sub> = 1 mV.

- 6. F<sub>MOD</sub> = 1 kHz, MONO, and L = R unless noted otherwise.

- **7.** ∆f = 22.5 kHz.

- 8.  $|f_2 f_1| > 2$  MHz,  $f_0 = 2 \times f_1 f_2$ . 9.  $B_{AF} = 300$  Hz to 15 kHz, A-weighted.

- 10. At  $A_{OUT}\ensuremath{\text{pin}}$  .

- **11.** ∆f = 75 kHz.

#### Table 5. AM/SW Receiver Characteristics<sup>1, 2</sup>

(V<sub>DD</sub> = 2.7 to 3.6 V, TA = 0 to 70 °C)

| Parameter                                  | Symbol          | Test Condition                                   | Min | Тур | Max  | Unit              |

|--------------------------------------------|-----------------|--------------------------------------------------|-----|-----|------|-------------------|

| Input Frequency                            | f <sub>RF</sub> | Medium Wave (AM)                                 | 504 | —   | 1750 | kHz               |

|                                            |                 | Short Wave (SW)                                  | 2.3 | _   | 28.5 | MHz               |

| Sensitivity <sup>3,4,5</sup>               |                 | (S+N)/N = 26 dB                                  | —   | 30  | _    | μV EMF            |

| Large Signal Voltage Handling <sup>5</sup> |                 | THD < 8%                                         | —   | 300 |      | mV <sub>RMS</sub> |

| Power Supply Rejection Ratio <sup>5</sup>  |                 | $\Delta V_{DD}$ = 100 mV <sub>RMS</sub> , 100 Hz | —   | 40  | _    | dB                |

| Audio Output Voltage <sup>3,6</sup>        |                 |                                                  | —   | 54  | _    | mV <sub>RMS</sub> |

| Audio S/N <sup>3,4,6</sup>                 |                 |                                                  | —   | 45  | _    | dB                |

| Audio THD <sup>3,6</sup>                   |                 |                                                  | _   | 0.1 | _    | %                 |

| Antenna Inductance <sup>5,7</sup>          |                 |                                                  | 180 | _   | 450  | μH                |

Notes:

1. Additional testing information is available in "AN569: Si4831/35/36/20/24/25-DEMO Board Test Procedure." Volume = maximum for all tests. Tested at RF = 6 MHz.

2. To ensure proper operation and receiver performance, follow the guidelines in "AN738: Si4825/36-A Antenna, Schematic, Layout, and Design Guidelines." Silicon Laboratories will evaluate schematics and layouts for qualified customers.

- 3. FMOD = 1 kHz, 30% modulation, 2 kHz channel filter.

- **4.**  $B_{AF}$  = 300 Hz to 15 kHz, A-weighted.

- 5. Guaranteed by characterization.

- 6.  $V_{IN} = 5 \text{ mVrms}.$

- 7. Stray capacitance on antenna and board must be < 10 pF to achieve full tuning range at higher inductance levels.

#### **Table 6. Reference Clock and Crystal Characteristics**

(V<sub>DD</sub> = 2.7 to 3.6 V, T<sub>A</sub> = 0 to 70 °C)

| Parameter                                        | Symbol          | Test Condition    | Min  | Тур    | Max | Unit |  |  |

|--------------------------------------------------|-----------------|-------------------|------|--------|-----|------|--|--|

|                                                  | Reference Clock |                   |      |        |     |      |  |  |

| XTALI Supported Reference Clock<br>Frequencies   |                 |                   | _    | 32.768 | _   | kHz  |  |  |

| Reference Clock Frequency<br>Tolerance for XTALI |                 |                   | -100 | —      | 100 | ppm  |  |  |

|                                                  | C               | rystal Oscillator |      |        |     |      |  |  |

| Crystal Oscillator Frequency                     |                 |                   | _    | 32.768 | _   | kHz  |  |  |

| Crystal Frequency Tolerance                      |                 |                   | -100 | _      | 100 | ppm  |  |  |

| Board Capacitance                                |                 |                   | _    | _      | 3.5 | pF   |  |  |

#### Table 7. Thermal Conditions

| Parameter                                                                                               | Symbol         | Min | Тур | Мах | Unit |  |  |

|---------------------------------------------------------------------------------------------------------|----------------|-----|-----|-----|------|--|--|

| Thermal Resistance*                                                                                     | $\theta_{JA}$  | —   | 80  | _   | °C/W |  |  |

| Ambient Temperature                                                                                     | T <sub>A</sub> | 0   | 25  | 70  | °C   |  |  |

| Junction Temperature                                                                                    | TJ             |     |     | 77  | °C   |  |  |

| *Note: Thermal resistance assumes a multi-layer PCB with the exposed pad soldered to a topside PCB pad. |                |     |     |     |      |  |  |

#### Table 8. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                   | Symbol           | Value       | Unit            |

|-----------------------------|------------------|-------------|-----------------|

| Supply Voltage              | V <sub>DD</sub>  | -0.5 to 5.8 | V               |

| Input Current <sup>3</sup>  | I <sub>IN</sub>  | 10          | mA              |

| Operating Temperature       | T <sub>OP</sub>  | -40 to 95   | °C              |

| Storage Temperature         | T <sub>STG</sub> | -55 to 150  | °C              |

| RF Input Level <sup>4</sup> |                  | 0.4         | V <sub>PK</sub> |

Notes:

1. Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure beyond recommended operating conditions for extended periods may affect device reliability.

2. The Si4825 devices are high-performance RF integrated circuits with certain pins having an ESD rating of < 2 kV HBM. Handling and assembly of these devices should only be done at ESD-protected workstations.

3. For input pins RST, VOL+, VOL-, XTALO, XTALI, BAND, TUNE2, TUNE1, LNA\_EN.

4. At RF input pins, FMI and AMI.

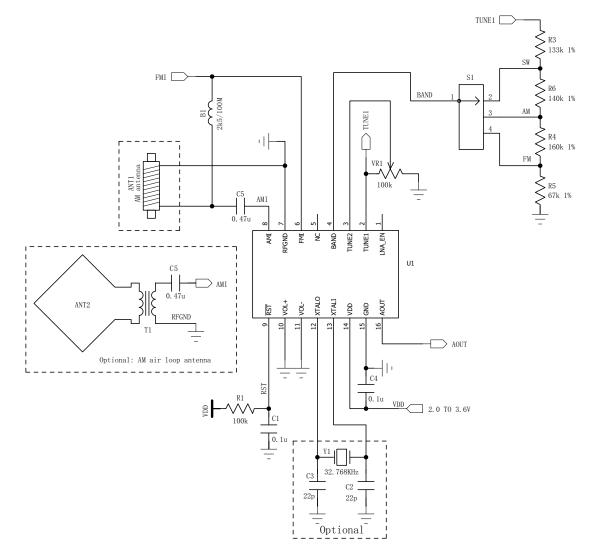

### 2. Typical Application Schematic

#### Notes:

- 1. Place  $C_4$  close to  $V_{DD}$  and GND pins.

- 2. Pin 15 GND connects directly to GND plane on PCB.

- 3. Pin 5 leave floating.

- To ensure proper operation and receiver performance, follow the guidelines in "AN738: Si4825/36-A Antenna, Schematic, Layout, and Design Guidelines." Silicon Labs will evaluate the schematics and layouts for qualified customers.

- 5. Pin 6 connects to the FM antenna interface and pin 8 connects to the AM antenna interface.

- 6. Place Si4825 as close as possible to antenna jack and keep the FMI and AMI traces as short as possible.

- 7. Recommend keeping the AM ferrite loop antenna at least 5 cm away from the tuner chip.

- 8. Keep the AM ferrite loop antenna at least 5 cm away from MCU, audio AMP, and other circuits which have AM interference.

- 9. Place the transformer T1 away from any sources of interference and even away from the I/O signals of the Si4825.

# 3. Bill of Materials

| Component(s) | Value/Description                                                                     | Supplier                    |

|--------------|---------------------------------------------------------------------------------------|-----------------------------|

| C1           | Reset capacitor 0.1 µF, ±20%, Z5U/X7R                                                 | Murata                      |

| C4           | Supply bypass capacitor, 0.1 µF, ±20%, Z5U/X7R                                        | Murata                      |

| C5           | Coupling capacitor, 0.47 µF, ±20%, Z5U/X7R                                            | Venkel                      |

| B1           | Ferrite bead 2.5 k/100 MHz                                                            | Murata                      |

| VR1          | Variable resistor (POT), 100 kΩ, ±10%                                                 | Kennon                      |

| R1           | Reset timing resistor, 100 k $\Omega$ , ±5%                                           | Venkel                      |

| R3           | Resistor, 133 kΩ, ±1%,                                                                | Venkel                      |

| R4           | Resistor, 160 kΩ, ±1%                                                                 | Venkel                      |

| R5           | Resistor, 67 kΩ, ±1%                                                                  | Venkel                      |

| R6           | Resistor,140 kΩ, ±1%                                                                  | Venkel                      |

| U1           | Si4825-A AM/FM/SW Analog Tune Analog Display Radio Tuner                              | Silicon<br>Laboratories     |

| S1           | Band switch                                                                           | Any, depends<br>on customer |

| ANT1         | Ferrite stick,180-450 µH                                                              | Jiaxin                      |

|              | Optional Components                                                                   | ·                           |

| C2, C3       | Crystal load capacitors, 22 pF, ±5%, COG<br>(Optional: for crystal oscillator option) | Venkel                      |

| Y1           | 32.768 kHz crystal (Optional: for crystal oscillator option)                          | Epson or equiv-<br>alent    |

| ANT2         | Air loop antenna, 10–20 µH                                                            | Various                     |

#### Table 9. Si4825-A Bill of Materials

### 4. Functional Description

Figure 2. Si4825 Functional Block Diagram

#### 4.1. Overview

The Si4825 is the entry level mechanical-tuned digital CMOS AM/FM/SW radio receiver IC that integrates the complete receiver function from antenna input to audio output. The Si4825 extends Silicon Laboratories multiband tuner family, and further increases the ease and attractiveness of design radio reception to audio devices through small size and board area, minimum component count, and superior, proven performance. The Si4825 requires a simple application circuit, and removes any requirements for manually tuning components during the manufacturing process.

Leveraging Silicon Laboratories' proven and patented digital low intermediate frequency (low-IF) receiver architecture, the Si4825 delivers desired RF performance and interference rejection in AM, FM, and SW bands. The high integration and complete system production test simplifies design-in, increases system quality, and improves manufacturability.

#### 4.2. FM Receiver

The Si4825 integrates a low noise amplifier (LNA) supporting the worldwide FM broadcast band (64 to 109 MHz) and the TV audio stations within the frequency range in China area are also supported.

Pre-emphasis and de-emphasis is a technique used by FM broadcasters to improve the signal-to-noise ratio of FM receivers by reducing the effects of high frequency interference and noise. When the FM signal is transmitted, a pre-emphasis filter is applied to accentuate the high audio frequencies. All FM receivers incorporate a de-emphasis filter which attenuates high frequencies to restore a flat frequency response. Two time constants are used in various regions. The de-emphasis time constant can be chosen to be 50 or 75  $\mu$ s.

#### 4.3. AM Receiver

The highly integrated Si4825-A10 supports worldwide AM band reception from 504 to 1750 kHz with five subbands using a digital low-IF architecture with a minimum number of external components and no manual alignment required. This patented architecture allows for high-precision filtering, offering excellent selectivity and SNR with minimum variation across the AM band. The Si4825 supports the worldwide AM band with five sub-bands. One of the bands is a universal AM band (AM4, 520–1730 kHz) supporting both 9 kHz and 10 kHz channel spaces for all regional AM standards of the world. Similar to the FM receiver, the Si4825-A10 optimizes sensitivity and rejection of strong interferers, allowing better reception of weak stations.

To offer maximum flexibility, the receiver supports a wide range of ferrite loop sticks from  $180-450 \mu$ H. An air loop antenna is supported by using a transformer to increase the effective inductance from the air loop. Using a 1:5 turn ratio inductor, the inductance is increased by 25 times and easily supports all typical AM air loop antennas, which generally vary between 10 and 20  $\mu$ H.

#### 4.4. SW Receiver

The Si4825 supports 36 short wave (SW) band receptions from 2.3 to 28.5 MHz, 18 of which are meter wave band (Narrow), and the rest of the SW bands are with wider frequency range that can be used in SW radio with 1 or 2 SW bands. Si4825 supports extensive short wave features such as minimal discrete components and no factory adjustments. The Si4825 supports using the FM antenna to capture short wave signals.

### 4.5. Frequency Tuning

A valid channel can be found by tuning the potentiometer that is connected to the TUNE1 and TUNE2 pin of the Si4825-A10 chip.

#### 4.6. Band Select

The Si4825-A10 supports worldwide AM band with five sub-bands, US/Europe/Japan/China FM band with five sub-bands, and SW band with 36 sub-bands. For details on band selection, refer to "AN738: Si4825/36-A Antenna, Schematic, Layout, and Design Guidelines."

#### 4.7. Volume Control

The Si4825 not only allows customers to use the traditional PVR wheel volume control through an external speaker amplifier, it also supports direct digital volume control through pins 10 and pin 11 by using volume up and down buttons. Refer to "AN738: Si4825/36-A Antenna, Schematic, Layout, and Design Guidelines."

#### 4.8. Reset, Powerup, and Powerdown

Setting the RSTB pin low will disable analog and digital circuitry, reset the registers to their default settings, and disable the bus. Setting the RSTB pin high will bring the device out of reset.

Figure 1 shows typical reset, startup, and shutdown timings for the Si4825. RSTB must be held low (asserted) during any power supply transitions and kept asserted as specified in Figure 1 after the power supplies are ramped up and stable. Failure to assert RSTB as indicated here may cause the device to malfunction and may result in permanent device damage.

A powerdown mode is available to reduce power consumption when the part is idle. Putting the device in powerdown mode will disable analog and digital circuitry while keeping the bus active.

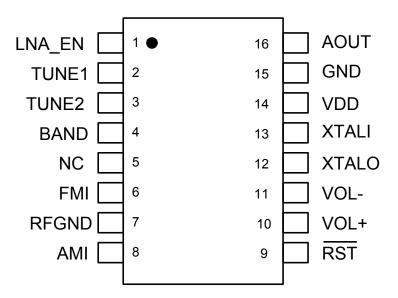

# 5. Pin Descriptions: Si4825-A10

| Pin Number(s) | Name   | Description                                                 |

|---------------|--------|-------------------------------------------------------------|

| 1             | LNA_EN | Enable SW external LNA.                                     |

| 2             | TUNE1  | Frequency tuning                                            |

| 3             | TUNE2  | Frequency tuning                                            |

| 4             | BAND   | Band selection and de-emphasis selection                    |

| 5             | NC     | No connect. Leave floating.                                 |

| 6             | FMI    | FM RF inputs. FMI should be connected to the antenna trace. |

| 7             | RFGND  | RF ground. Connect to ground plane on PCB.                  |

| 8             | AMI    | AM RF input. AMI should be connected to the AM antenna.     |

| 9             | RST    | Device reset (active low) input                             |

| 10            | VOL+   | Volume button up                                            |

| 11            | VOL-   | Volume button down                                          |

| 12            | XTALO  | Crystal oscillator output                                   |

| 13            | XTALI  | Crystal oscillator input/external reference clock input     |

| 14            | VDD    | Supply voltage. May be connected directly to battery.       |

| 15            | GND    | Ground. Connect to ground plane on PCB.                     |

| 16            | AOUT   | Audio output                                                |

### 6. Ordering Guide

| Part Number <sup>1,2</sup> | Description                                         | Package<br>Type     | Operating<br>Temperature/Voltage |

|----------------------------|-----------------------------------------------------|---------------------|----------------------------------|

| Si4825-A10-CS              | AM/FM/SW Broadcast Radio Receiver                   | 16L SOIC<br>Pb-free | 0 to 70 °C<br>2.0 to 3.6 V       |

|                            | the end of the device part number to denote tape an |                     | vices will typically operate at  |

25 °C with degraded specifications for V<sub>DD</sub> voltage ramped down to 2.0 V.

2. The -C suffix in the part number indicates Consumer Grade product. Please visit www.silabs.com to get more information on product grade specifications.

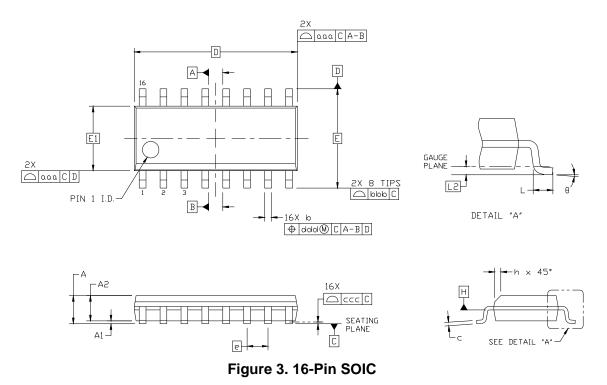

# 7. Package Outline: Si4825-A10

The 16-pin SOIC illustrates the package details for the Si4825-A10. Table 10 lists the values for the dimensions shown in the illustration.

| Dimension | Min      | Max  |

|-----------|----------|------|

| А         | _        | 1.75 |

| A1        | 0.10     | 0.25 |

| A2        | 1.25     | —    |

| b         | 0.31     | 0.51 |

| С         | 0.17     | 0.25 |

| D         | 9.90 BSC |      |

| E         | 6.00 BSC |      |

| E1        | 3.90 BSC |      |

| е         | 1.27 BSC |      |

| L         | 0.40     | 1.27 |

| L2        | 0.25 BSC |      |

| h         | 0.25     | 0.50 |

| θ         | 0°       | 8°   |

| aaa       | 0.10     |      |

| bbb       | 0.20     |      |

| CCC       | 0.10     |      |

| ddd       | 0.25     |      |

#### **Table 10. Package Dimensions**

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 8. PCB Land Pattern: Si4825-A10

Figure 4, "PCB Land Pattern," illustrates the PCB land pattern details for the Si4825-A10-CS SOIC. Table 11 lists the values for the dimensions shown in the illustration.

Figure 4. PCB Land Pattern

#### Table 11. PCB Land Pattern Dimensions

| Dimension                                                                                                                                                                                                                                                                                          | Feature            | (mm) |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--|--|

| C1                                                                                                                                                                                                                                                                                                 | Pad Column Spacing | 5.40 |  |  |

| E                                                                                                                                                                                                                                                                                                  | Pad Row Pitch      | 1.27 |  |  |

| X1                                                                                                                                                                                                                                                                                                 | Pad Width          | 0.60 |  |  |

| Y1                                                                                                                                                                                                                                                                                                 | Pad Length         | 1.55 |  |  |

| <ul> <li>Notes:</li> <li>1. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X165-16N for Density Level B (Median Land Protrusion).</li> <li>2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.</li> </ul> |                    |      |  |  |

# 9. Top Marking

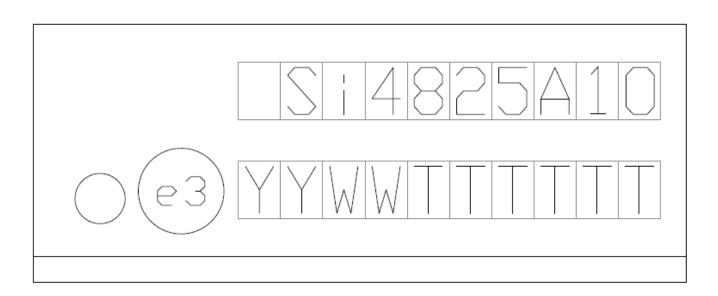

### 9.1. Si4825-A10 Top Marking

### 9.2. Top Marking Explanation

| Mark Method:        | Laser                               |                                                                                         |  |

|---------------------|-------------------------------------|-----------------------------------------------------------------------------------------|--|

| Pin 1 Mark:         | Mold Dimple (Bottom-Left Corner)    |                                                                                         |  |

| Font Size:          | 0.71 mm (2.0 Point) Right-Justified |                                                                                         |  |

| Line 1 Mark Format: | Custom Part Number                  | Si4825A10                                                                               |  |

|                     | Circle = 1.3 mm Diameter            | "e3" Pb-Free Symbol                                                                     |  |

| Line 2 Mark Format: |                                     | Assigned by the Assembly House. Corresponds to the year and work week of the mold date. |  |

|                     | TTTTTT = Manufacturing code         | Manufacturing Code from the Assembly Purchase<br>Order form.                            |  |

## **10. Additional Reference Resources**

Contact your local sales representatives for more information or to obtain copies of the following references:

- AN738: Si4825/36-A Antenna, Schematic, Layout, and Design Guidelines

- AN569: Si4831/35/36/20/24/25-DEMO Board Test Procedure

- Si4825-DEMO Board User's Guide

# **DOCUMENT CHANGE LIST**

### **Revision 0.1 to Revision 0.8**

- Updated Table 1, "Recommended Operating Conditions"

- Updated Table 2, "DC Characteristics"

- Updated Table 4, "FM Receiver Characteristics"

- Updated Table 5, "AM/SW Receiver Characteristics"

- Updated Section "4.3. AM Receiver"

- Updated Section "10. Additional Reference Resources"

- Section 5 "Pin Descriptions: Si4825-A10"

### **Revision 0.8 to Revision 1.0**

- Updated Table 3. "Reset Timing Characteristics"

- Inserted Section 4.8. "Reset, Powerup, and Powerdown"

# **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Email: FMinfo@silabs.com Internet: www.silabs.com

#### Patent Notice

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analogintensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Silicon Laboratories: Si4825-A10-CSR Si4825-A10-CS